University of Jordan Faculty of Graduate Studies

2002

# DESIGN AND CONSTRUCTION OF A PROTOTYPE PROGRAMMABLE LOGIC CONTROLLER .

BY

Mohammad Usama Kamal Tahboub

**SUPERVISOR**

Dr. Khaled Toukan

Jed color sulfate services

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE IN INDUSTRIAL ENGINEERING, FACULTY OF GRADUATE STUDIES, UNIVERSITY OF JORDAN.

January, 1994

# This thesis was defended successfully on January 10, 1994.

### Committee Names

- 1- Dr. Khaled Toukan

- 2- Dr. Yousef Al-assaf

- 3- Dr. Souheil Odeh

### Signature

Khaled Toukan less at a

Souhiel Odeh

# **DEDICATION**

اهــــداء

الى أمــي التي وهبتني الكثير ...

## **ACKNOWLEDGEMENTS**

# شكر و تقدير

الحمد للـــه أولا و آخرا على نعمائه و توفيقه .

اود أن أتقدم بالتقدير و الأحترام و الشكر الجزيل للدكتور خالد طوقان الذي أبدى اهتماما صادقا و جهدا مشكورا خلال مراحل العمل المختلفه ، كما أتقدم بالشكر للدكتور يوسف العساف و الدكتور سهيل عوده على حسن اهتمامهما و تقدير هما لهذا العمل . أود أن أتقدم بالشكر أيضا لكل من الدكتور خلاون طهبوب و الدكتور عبد الرحمن جرادات و الدكتور صباح البيرماني لما أبدوا من ملاحظات مفيده واهتمام مشكور . كما أود أن أشكر المهندس كمال عمار و المهندس سامح عليان وللسيد محمد فوزي و كل من أبدى جهدا و اهتماما ساعد على انجاز هذه الرسالة .

و أخيرا أتقدم بالشكر لعائلتي التي وقفت الى جانبي منذ اللحظات الأولى تدعمني و تحفزني و تدفعني الى الأمام .

| Committee Decisionii                            |   |

|-------------------------------------------------|---|

| Dedicationiii                                   |   |

| Acknowledgmentsiv                               |   |

| Contents v                                      |   |

| List of Tables vii                              | i |

| List of Figures x                               |   |

| Abstract ( In English ) xii                     |   |

| Chapter One: Introduction                       |   |

| 1.1. Historical Background 1                    |   |

| 1.2. PLCs in Jordan 5                           |   |

|                                                 |   |

| Chapter Two: PLC Structure                      |   |

| 2.1. Central Processing Unit                    |   |

| 2.1.1. The Processor                            |   |

| 2.1.2. The Memory                               |   |

| 2.1.3. The Power Supply                         |   |

| 2.2. The Input / Output System 18               |   |

| 2.2.1. Discrete Inputs / Outputs 18             |   |

| 2.2.2. Numerical Inputs / Outputs 21            |   |

| 2.2.3. Special Inputs / Outputs 22              |   |

| 2.2.4. Remote Inputs / Outputs 24               |   |

| Chapter Three: PLC Products and Applications 25 |   |

| 3.1. PLC Families                               |   |

| 3.2. Defining the Control System 27             |   |

| 3.3. Steps to Implement a PLC System 30         |   |

| 3.4. PLC Applications                           |   |

#### CONTENTS

| ONTENTS | PAGE |

|---------|------|

|         |      |

| 3.4.1. Rubber and Plastic                  | 34 |

|--------------------------------------------|----|

| 3.4.2. Chemical and Petrochemical          | 35 |

| 3.4.3. Power                               | 35 |

| 3.4.4. Metals                              | 36 |

| 3.4.5. Materials Handling                  | 37 |

| 3.4.6. Automotive                          | 38 |

| 3.4.7. Manufacturing / Machining           | 38 |

| 3.4.8. Examples                            | 39 |

| Chapter Four : Hardware Design             | 42 |

| 4.1. The Central Processing Unit ( CPU )   | 42 |

| 4.2. Input / Output ( I/O ) Interface      | 43 |

| 4.2.1. Input / Output Interface Card       | 44 |

| 4.2.1.1. Buffer Stage                      | 45 |

| 4.2.1.2. Decoding Stage                    | 47 |

| 4.2.1.3. Peripheral Devices Stage          | 48 |

| 4.2.2. Power Amplification Card            | 60 |

| 4.3. Hardware Set Up                       | 71 |

| 4.4. Reading The Inputs                    | 72 |

| 4.5. Updating The Outputs                  | 73 |

| Chapter Five : Software Design             | 75 |

| 5.1. Programming Language Used             | 75 |

| 5.2. Menu System                           | 75 |

| 5.3. Boolean Language                      | 76 |

| 5.4. User Program Translation              | 77 |

| 5.5. Running User Program                  |    |

| 5.5.1. Memory Configuration and Peripheral |    |

| CONTENT | S |

|---------|---|

|---------|---|

# PAGE

|             | · · · · · · · · · · · · · · · · · · · |     |

|-------------|---------------------------------------|-----|

|             | Devices Set Up                        | 80  |

| !           | 5.5.2. Scanning                       | 82  |

|             | 5.5.2.1. Reading The Inputs           | 82  |

|             | 5.5.2.2. Executing The User Program   | 83  |

|             | 5.5.2.3. Updating The Outputs         | 85  |

| 5.6.        | Boolean Language Rules                | 86  |

| 5.7.        | Programs' Listing                     | 89  |

| Chapter Siz | c : Testing and Equipment             | 90  |

| 6.1.        | PLC Components                        | 90  |

| 6.2.        | Cost Estimation                       | 90  |

| 6.3.        | Testing Basic Operation               | 93  |

| 6.4.        | Traffic Light System                  | 93  |

| 6.5.        | Conclusion                            | 94  |

| APPENDIX A  | ••••••                                | 96  |

| APPENDIX B  | ********************************      | 103 |

| APPENDIX C  | **************                        | 113 |

| APPENDIX D  | •••••••••••••                         | 118 |

| APPENDIX E  | ••••••                                | 131 |

| References  | *************                         | 140 |

| Abstract (  | In Arabic )                           | 142 |

#### List of Tables

| 1.1   | Typical PLC Features / Benefits                | 6  |

|-------|------------------------------------------------|----|

| 2.1   | Discrete Input / Output Devices                | 19 |

| 2.2   | Standard I/O Voltage Ratings of                |    |

|       | Discrete I/O Interfaces                        | 20 |

| 3.1   | Steps for Selecting the Right PLC              | 31 |

| 4.1   | Components of the Interface Card               | 45 |

| 4.2   | 8255A Basic Operation                          | 52 |

| 4.3   | Mode 0 Port Definition of the PPI              | 55 |

| 4.4   | Register Selection Table                       | 58 |

| 5.1   | Boolean Language ( Mnemonics and Operators ) . | 78 |

| 5.2   | Sizes ( in Bytes ) of Programs Developed       | 89 |

| 6.1   | Components Listing                             | 91 |

| A.1.1 | Typical Standard Features of                   |    |

|       | Small PLCs                                     | 96 |

| A.2.1 | Typical Standard Features of                   |    |

|       | Medium PLCs                                    | 97 |

| A.3.1 | Typical Standard Features of                   |    |

|       | Large PLCs                                     | 99 |

| A.4.1 | Typical Standard Features of                   |    |

|       | Very Large PLCs 1                              | 01 |

| B.1.1 | Function Table of the 74LS245 1                | 04 |

| B.1.2 | Recommended Operating Conditions               |    |

|       | of the 74LS245 1                               | 04 |

| B.2.1 | Recommended Operating Conditions |     |

|-------|----------------------------------|-----|

|       | of the 74LS244                   | 106 |

| B.3.1 | Function Table of the 74LS85     | 108 |

| B.3.2 | Recommended Operating Conditions |     |

|       | of the 74LS85                    | 109 |

| B.4.1 | Function Table of the 74LS138    | 111 |

| B.4.2 | Recommended Operating Conditions |     |

|       | of the 74LS138                   | 112 |

| C.2.1 | Data Sheets of the MOC3031       |     |

|       | Opto-Coupled Triac               | 117 |

## List of Figures

| 2.1   | Block Diagram of the PLC                       | 10 |

|-------|------------------------------------------------|----|

| 2.2   | Scanning                                       | 11 |

| 2.3   | A PLC Memory Map                               | 14 |

| 2.4   | Memory Area Table of the Data Table            | 16 |

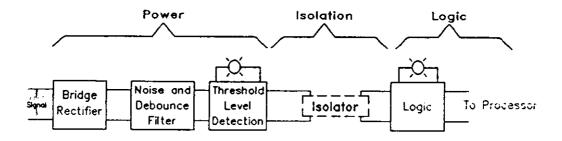

| 2.5   | Block Diagram of the AC/DC Input Circuit       | 21 |

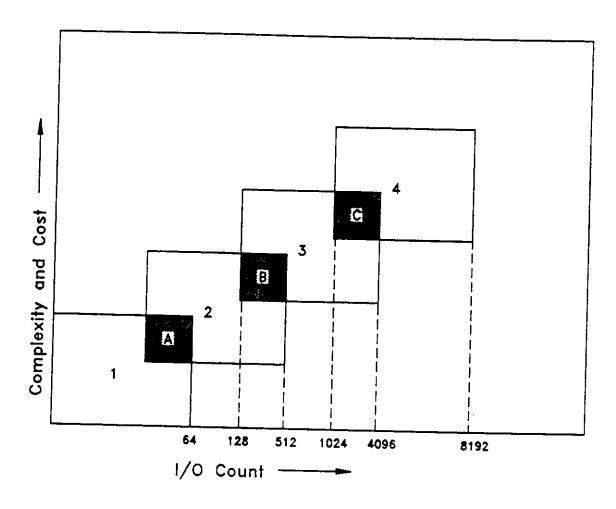

| 3.1   | Illustration of the PLC Product Range          | 26 |

| 3.2   | Control Type Configuration                     | 29 |

| 4.1   | Block Diagram of the I/O Module                | 43 |

| 4.2   | Schematic Diagram of the I/O Interface Card    | 46 |

| 4.3   | Block Diagram of the PPI                       | 50 |

| 4.4   | Mode Definition Format of the PPI              | 54 |

| 4.5   | Block Diagram of the 8253 Timer / Counter      | 56 |

| 4.6   | Control Word Format of the PPI                 | 59 |

| 4.7   | Timing Diagram for Mode 0 Operation            | 61 |

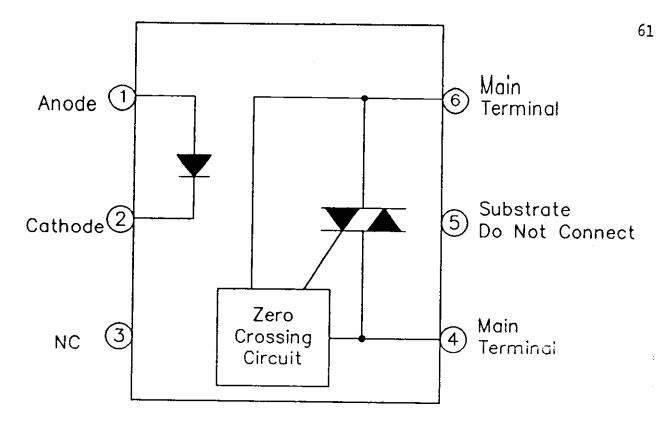

| 4.8   | MOC3031 Opto-Coupled Triac                     | 62 |

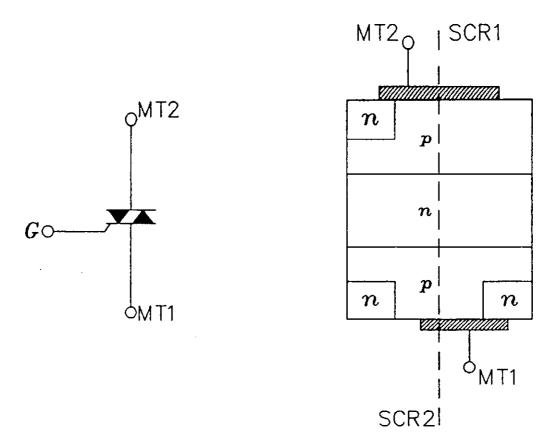

| 4.9.a | Triac Symbol                                   | 63 |

| 4.9.b | Triac Structure                                | 63 |

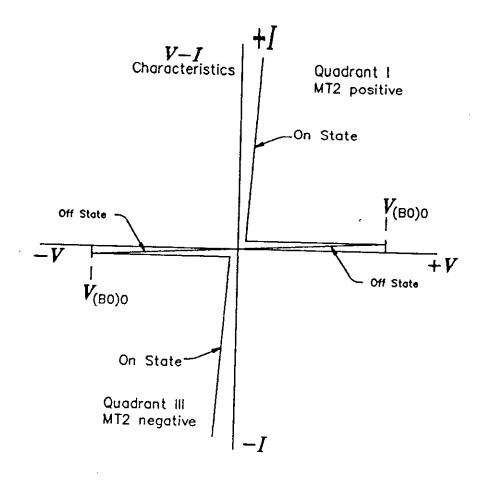

| 4.10  | Voltage-Current Characteristics of the Triac . | 64 |

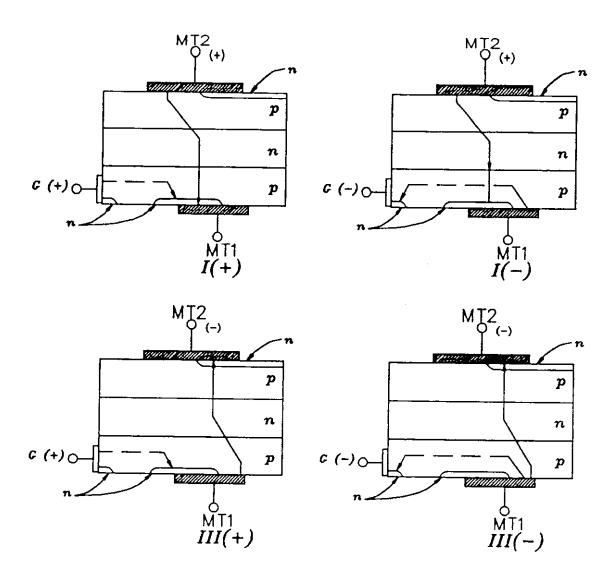

| 4.11  | Modes of Operation of the Triac                | 66 |

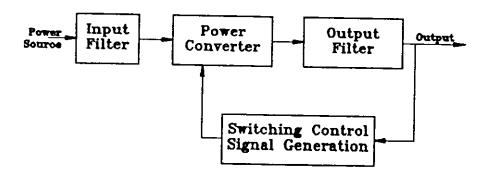

| 4.12  | Generalized Power Converter Structure          | 66 |

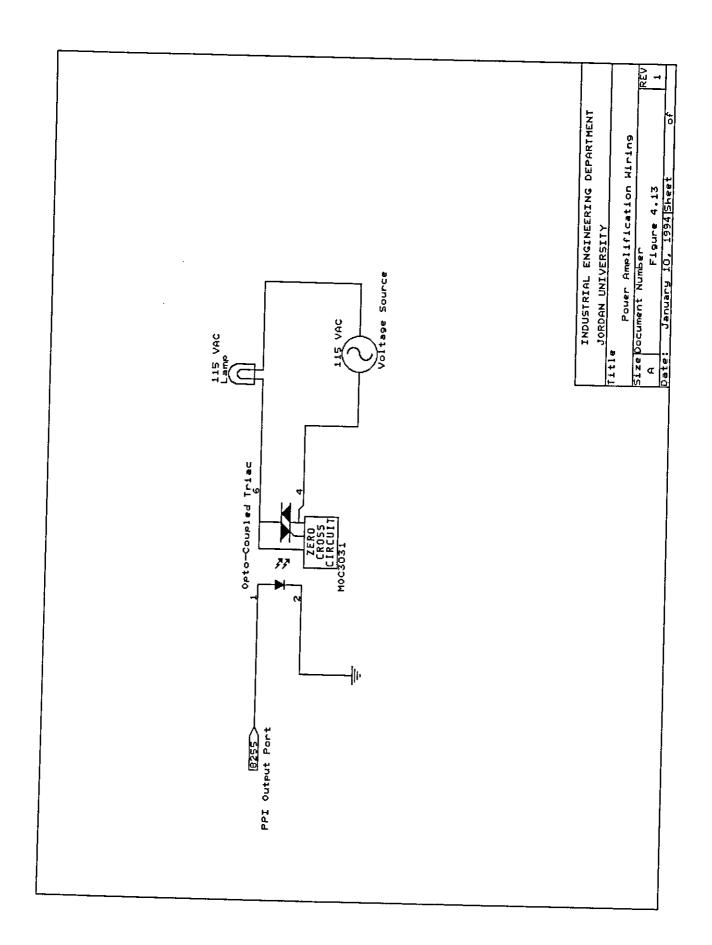

| 4.13  | Power Amplification Wiring                     | 70 |

| 5.1   | Menu System Options                            | 76 |

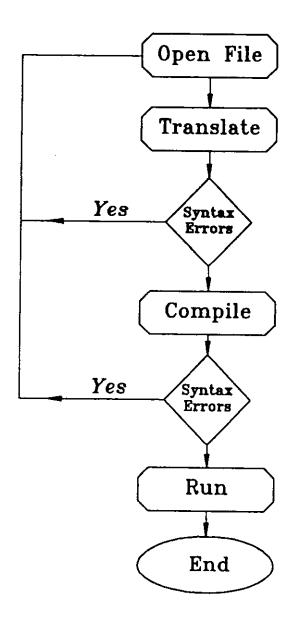

| 5.2   | Implementation Stages of a User Program        | 81 |

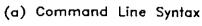

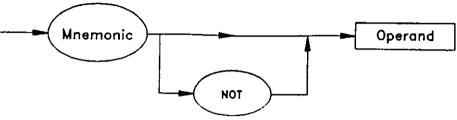

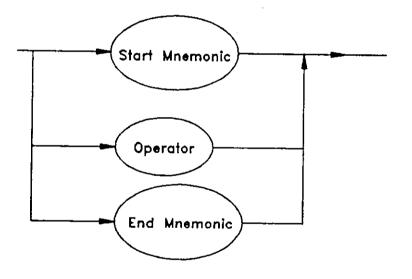

| 5.3   | Boolean Language Syntax Diagrams               | 87 |

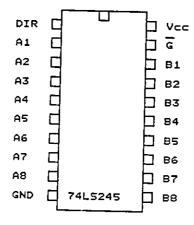

| B.1.1 | Pin Diagram of the 74LS245   | 103 |

|-------|------------------------------|-----|

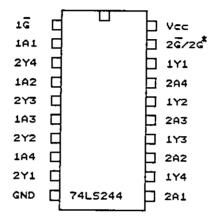

| B.2.1 | Pin Diagram of the 74LS244   | 105 |

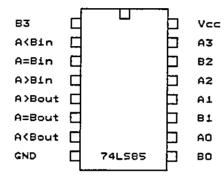

| B.3.1 | Pin Diagram of the 74LS85 1  | 107 |

| B.4.1 | Pin Diagram of the 74LS138 1 | 110 |

### **ABSTRACT**

# Design and Construction of a Prototype Programmable Logic Controller

By : Mohammad Tahboub Supervisor : Dr. Khaled Toukan

In this thesis, a step towards increasing the national 'Know - How' of Programmable Logic Controllers (PLCs) is undertaken . The concept of operation of the PLC is , first, described; a discussion of the major components, different features and fields of application is also included . A prototype PLC is, then, designed and constructed through two parallel, interrelated procedures: hardware design and software development . A prototype PLC is designed and constructed using the CPU of a personal computer, to provide for the processor and power supply of the PLC, and an I/O interface module that provides twelve discrete output signals at 115 VAC and twelve discrete input signals at TTL level . The I/O interface module consists of two major parts: the I/O interface card and the DC / AC power converter . A Boolean Language environment is developed using Turbo Pascal (version 6) . The developed environment provides the user with the ability to write user programs in Boolean Language, translate the user program into Pascal, compile the translated Pascal code, and run the compiled programs. Running a user program results in two main activities: 1) set up of the prototype PLC and 2) performing continuous scanning . Thorough testing of the prototype PLC is performed at both TTL level and 115 VAC level to check for proper operation .

#### Chapter One

#### Introduction

#### 1.1. Historical Background

Relay controlled systems were inflexible and costly . The need for a system that provides for :

- 1- computer flexibility,

- 2- easy programming and maintenance,

- 3- reusability ,

- 4- robustness in the industrial environment, and

- 5- reduction in down time of machines ,

led to the design criteria of the first programmable logic controller ( PLC ) in 1968 by the Hydramatic division of the General Motors corporation [1] .

The first programmable logic controllers were limited to applications such as transfer lines and grinding machines since they were capable of on/off control only. However, they were easily installed, needed less space and energy than relays, and were reusable.

As time went, great enhancements were made to PLCs:

1- Early innovations ( 1970 - 1974 ) in microprocessor technology added greater flexibility and intelligence to the PLC. The PLC became capable of interfacing with the operator, manipulating data, performing arithmetic operations, and communicating with computers [1].

2- Later enhancements ( 1975-1979 ) in hardware and software provided more flexibility to the PLC. The PLC provided larger memory capacity, remote Input/Output capabilities, analog control capability, operator

communication capability , and user friendly software environments [1] .

Larger memory capacity meant larger application programs and larger amounts of data that could be held and manipulated .

Remote input / output was done by signal multiplexing over two twisted pairs of wires . This made it possible for large systems to be divided into smaller systems; smaller systems are more flexible and can be maintained easily .

Development of communication capabilities of the PLC made it possible for users to get their PLCs interconnected through Local Area Networks ( LANs ) in a step towards having a complete flexible manufacturing system.

Software enhancements provided easy utilization of hardware enhancements. Such software enhancements included the use of computer like statements and menu driven software. 431757

3- Later ( 1980 - 1989 ) , PLCs were greatly enhanced both in hardware and software capabilities .

Hardware enhancements include the achievement of faster scan times; availability of special interfaces that allow certain devices to be connected directly to the controller, such as thermocouplers and strain gauges, and existence of a wide range of PLC sizes that provides the user with a variety of options.

Software enhancements include the use of high level languages such as Basic , diagnostics and fault detection of both the controller and the controlled machine , and support of floating point mathematics which facilitates.

performing complex computations [1] .

4- Nowadays ( 1990 - 1993 ) , Program generators are now being developed for PLCs . They help programmers to overcome the complications associated with data addressing and the inconveniences of bit addressing . The programmer has to provide the initial program specifications only and the generator performs the rest of job .

First , the programmer has to identify the devices and switches of the application . Second , he / she has to define the conditions under which each device will change state . Third , the PLC program generator takes over and generates the program code by first translating each state change condition into one or more rungs of the program ladder diagram and , next , assigning valid data addresses to each of the devices / switches defined [2] .

However, the above mentioned code generators do not provide portability of code between the different PLCs; both the generator and generated code are PLC dependent. Another approach is to develop an automatic PLC program generator with a standard interface; it aims at improving the portability of PLC programs developed on different PLCs [3].

Such a generator was developed by Sangecta Bhatnager and Richard T. Lion in 1990 [3] . It consists of six modules , some of which are PLC dependent and some are not . The generator translates the user program specification into a Standard Control Logic Specification ( SCLS ) that is portable between different PLCs . Next , the generator generates a PLC specific program code to be

executed .

Bidirectional conversion of program code between SCLS specification and executable code is available; thus, portability is improved.

PLC simulators is another field of concern for the time being . Different microcomputer based simulators of PLCs are developed that provide a safe , reliable testing environment of newly developed user programs . Such simulators are also useful for training purposes .

Testing user programs is time consuming; on line testing would increase equipment down-time. Moreover, on line testing increases the probability of damage of hardware equipment connected to the PLC. Such disadvantages are overcome by using PLC simulators [4].

PCL ( Programmable Controller Language ) is a high level , real-time programming language developed in the Technical University of Istanbul , Turkey Ιt is syntactically similar to Pascal Ιt provides structured data types , efficient control structures , concurrent processing , exception handling and asynchronous events Ιt is suitable for complex applications which require critical interrupt handling mechanisms [5] .

Generally speaking , the PLC is an essential part of factory automation . The PLC is , now , part of the integrated system combining robots , Computer Numerically Controlled ( CNC ) machines , CAD/CAM systems , and Management Information Systems ( MIS ) [1] .

When the PLC was compared versus relays , some

time ago , a trade-off was made between the cost of the PLC , relative to the relay system cost , and the features provided by the PLC such as flexibility , high reliability , small space requirements , and the ability to accommodate future expansion . However , as the cost of hardware is nowadays decreasing significantly and as the user is provided with the ability to choose the controller that suits him / her out of a wide range of controllers , the PLC appears to be the more probable choice .

Table 1.1 shows some of the PLC features and benefits.

#### 1.2. PLCs in Jordan:

Industrial organizations in Jordan can be categorized into three major types according to the technology they employ:

- (a) The first type of organizations uses up-to-date new technology in its production lines; these represent a small percentage out of the total. They usually suffer from the lack of an expert staff that can support and maintain the technology used.

- (b) The industrial organizations of the second type use what is called new-old technology; this is old technology that is out of date and is no more used in the developed countries' industry; thus; they are imported to be used in third world countries. This type represents a good percentage out of the total. Such organizations might face problems with future expansion and lack of spare parts.

- (c) The third type of organizations uses reconditioned old technology that usually requires extensive maintenance and

Table 1.1 Typical PLC Features / Benefits [1] .

| Inherent Features                        | Benefits                                                                                                 |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Solid-State Components                   |                                                                                                          |

| Solid-Scate Components                   | High Reliability                                                                                         |

| Programmable Memory                      | Simplifies Changes                                                                                       |

| <u>-</u>                                 | Flexible Control                                                                                         |

| Small Size                               | Minimum Space Requirements                                                                               |

| Microprocessor-Based                     | Communication Capability Higher Level of Performance Higher Quality Products Multi-functional Capability |

| Software Timers/Counters                 | Eliminate Hardware<br>Easily Changed Presets                                                             |

| Software Control Relays                  | Reduce Hardware/Wiring Cost<br>Reduce Space Requirements                                                 |

| Modular Architecture                     | Installation Flexibility<br>Easily Installed<br>Hardware Purchase Minimized<br>Expandability             |

| Variety of I/O Interface                 | Controls Variety of Devices<br>Eliminates Customized Control                                             |

| Remote I/O Stations                      | Eliminate Long Wire Problems                                                                             |

| Diagnostic Indicators                    | Reduce Trouble-Shooting Time<br>Signal Proper Operation                                                  |

| Modular I/O Interface                    | Neat Appearance of Control<br>Panel<br>Easily Maintained<br>Easily Wired                                 |

| All System Variables<br>Stored in Memory | Useful Management /<br>Maintenance Data<br>Report Generation                                             |

|                                          |                                                                                                          |

suffers from the lack of spare parts in both the national and international markets . Future expansion and development might require discarding the old technology and

replacing it with new technology .

In Jordan , there are some authorized dealers of international companies that have PLC products such as AEG / Modicon , Fuji Electric , and Allen-Bradely .

Worldwide speaking , Siemens is number one in the world in the field of PLCs . They have a worldwide marketshare of 25% and a Middle East marketshare of 45% . Their worldwide sales in 92/93 was one Billion US dollars . Allen-Bradely and Mitsubishi are the second and the third in the world , respectively .

AEG / Modicon is an international company that has a good share of the world market . It is a large company that has around 16,500 - 17,000 employees .

In 1991, AEG sales in automation systems were approximately 3000 billion Deutsche marks; automation systems include real time computers and PLCs as major items. AEG's annual report ensures that the AEG company is the leading supplier of integrated systems in Europe, North America, and South Asia. Foreign countries have a 44% share out of AEG product sales.

AEG's Jordanian authorized dealers have only installed 5-10 systems at different sites in Jordan . These include the Jordan Sewing and Weaving Company , the Sewage Treatment Plant in the Industrial City in Irbid , Al-Sufara Bakery , and the Arab Bank .

There are other sites in Jordan that use AEG's PLCs in automated factories; however, these PLC sites were imported as parts of complete solutions from Europe and were completely installed by foreign experts. Jordanian

authorized dealers are not referenced except for spare parts.

Fuji Electric is also an international Japanese company specialized in electric and electronic products. It is considered to be one of the top ten in the world in this field.

U.S.A. has a 50% share of Fuji's sales , Europe has 20% share , and a 30% share is left for Japan's internal market .

Fuji PLCs' authorized dealers in Europe are done through Germany. They are responsible for the Fuji PLC installations in third world countries including Jordan. Such sites include the 'Jordan Electricity Authority'.

As claimed by Fuji's authorized dealer in Jordan, Fuji company refuses to allow the Jordanian Fuji authorized dealer to deal with PLCs; Fuji company thinks it is too early for third world countries to deal with automation provided, also, that there is no qualified people in Jordan to support such technology.

In fact , Jordanian PLCs authorized dealers are facing many problems :

(a) Owners of new factories prefer to implement total solutions granted; they import ready-made factories to be installed in Jordan by foreign companies. This is more expensive and of less benefit to the Jordanian industry; consultation of Jordanian experts and national cooperation would result in identical solutions with less cost and would provide great benefits to the Jordanian Industrial 'Know - How'.

- (b) The new technology implemented in limited aspects in Jordan requires a highly qualified staff for support and maintenance, the lack of which is a real problem. This can be solved by supporting efficient training courses outside and inside Jordan; national co-operation is the key solution for such a problem.

- (c) The majority of Jordanian factories are based on old technology, as mentioned above, which is a real problem. The process of updating old technology to use the new technology, part of which is the PLC, is a difficult process that requires special interface stages to be accommodated with old technology logic and power requirements.

In Europe , wide markets , promising industry , and large money capitals allow for discarding the old technology and replacing it with new technology . This is not the case in Jordan .

This is a short overview of the PLC market in Jordan. As time goes, the need for co-operation between the different industrial national organizations increases in order to put the different efforts on the right track. A good step forward is accomplished if a qualified staff; that is capable of installing, testing, and maintaining PLCs in Jordan is being developed.

# <u>Chapter Two</u> <u>PLC Structure</u>

The programmable controller as defined by National Electrical Manufacturers Association ( NEMA ) is a : 'Digital electronic apparatus with a programmable memory for storing instructions to implement specific functions, such as logic sequencing, timing, counting, and arithmetics to control machines and processes '[1].

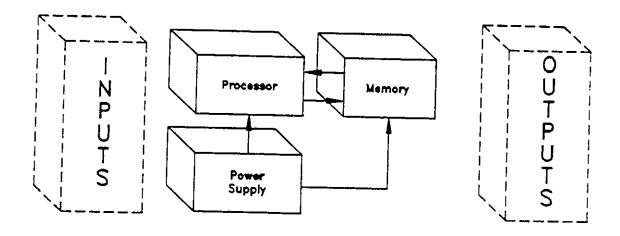

A PLC is composed mainly of two parts; these are the Central Processing Unit ( CPU ) and the input / output interface. The CPU gets its inputs from the outside world using the I/O interface, executes the stored program loaded in the memory, and sends appropriate output commands to control devices through the I/O interface. Figure 2.1 shows the block diagram of the PLC [1].

Figure 2.1 Block diagram of the PLC .

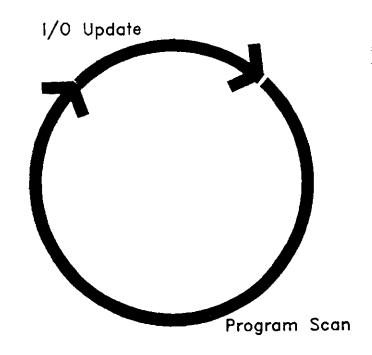

The process of reading the inputs , executing the loaded user program , and controlling outputs is called

'Scanning' and is performed in a continuous manner , as shown in figure 2.2 .

Figure 2.2 canning .

# 2.1. The Central Processing Unit (CPU):

The central processing unit consists of three major components: the processor, the memory, and the power supply.

### 2.1.1. The Processor:

The processor performs many tasks including the scanning process, the different communication processes, and the system diagnostics process [1].

Scanning is a cyclic process that is performed continuously with a cycle time depending on the power of the controller . A range of (1 - 100) msec is available, at different costs . Usually, manufacturers specify the scanning cycle time in terms of the amount of memory to be

scanned; for example, 10 msec / 1 K byte of scanned memory. Other factors, such as the existence of remote I/O or the use of CRTs to monitor the program, affect the scanning time, also.

The processor performs the scanning process by executing a set of internal permanent programs called the Executive [1].

Communication with remote I/O subsystems is another task of the processor [1]. Remote communication requires the existence of an I/O subsystem adapter module located in the CPU and the existence of a remote I/O processor module via which communication can be done.

Remote communication uses special cables such as twisted pair coaxial cables or fiber optic cables. Error detection and correction methods are implemented within the processor communication protocols; possible methods are parity checking, check sum, and Hamming code methods.

The processor is capable of performing diagnostics tests for the memory , battery , power supply , and itself. Some processors are even capable of performing diagnostics tests on the controlled machine [1] .

Categorization of the processors in PLCs can be done according to the configuration of the processor system implemented . Multi-Processing category , for example , tends to have small processors working in parallel in such a way that the different tasks are distributed among them and the processing time is reduced .

The data word is another basis of classifying processors; the data word represents the number of bits

that are treated as one unit by the processor .

### 2.1.2. <u>The Memory</u>:

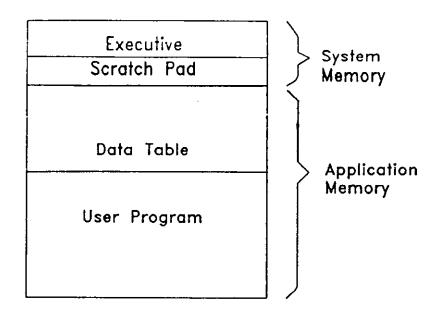

The memory of a PLC can be divided , according to its usage , into four types ; these are the Executive , the Scratch Pad , the User Program Memory, and the Data Table [1] .

The Executive is that region of the memory that contains the 'Executive 'which is the supervisory permanent programs that direct the system activities.

The Scratch Pad is a temporary storage used by the CPU to store data that are continuously processed and needed instantaneously. Access of the Scratch Pad is faster than access to the main memory.

User Program Memory is that part of the main memory that contains the program of user instructions .

The Data Table is a memory area that is used to store any data required by the scanning process. Such data include any data associated with the control program, such as timers / counters preset values, and the data representing the input / output status of the system.

Figure 2.3 shows a simple memory map of the PLC. The executive and scratch pad are called the 'System Memory'; they are parts of the memory that are transparent to the user. Both the data table and the user program memory are called the 'Application Memory' which is accessible to the user.

The data in the data table is treated in two different modes, status on / off mode and word ( or byte ) mode. In the status on / off mode, the data is treated

Figure 2.3 A PLC Memory Map [1] .

as single on / off bits each representing the status of a certain input , output , or memory address . In the word mode , bits of data are treated in groups representing words of data in Binary or Binary Coded Decimal ( BCD ) form [1] .

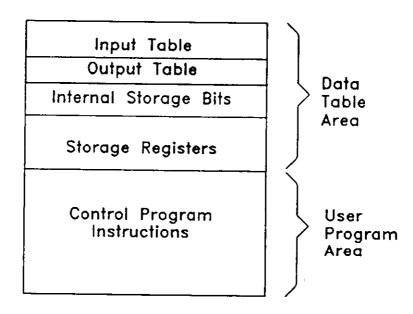

There are four types of data that are stored in the Data Table area according to which it can be functionally divided into [1]:

(a) Input table area: is a memory area (array of bits) used to reflect the status of input devices connected to the input interface; each bit in the input table corresponds to an input device. When the input device is switched 'ON', the corresponding address bit in the input table is switched to '1' (ON / True). The address bit is switched to '0' (OFF / False) when the input device is switched off. These input addresses are used by the 'Executive' when performing its scanning

process .

(b) Output table area: is a memory area (array of bits) that corresponds to each output device connected to the output interface. During the scanning process, the processor reads the inputs and executes the user control program; consequently, the output table is updated with ones and zeros.

Any output device with a memory bit set to ' 1 ' is switched ON . If the memory in the output table is ' 0 ', the corresponding device is switched OFF .

(c) Internal storage bits: is a memory area (array of bits) used in control programs as interlocks. They are treated in a similar manner as the bits in the output table; however, the main difference lies in that internal storage bits are not connected to output devices.

Internal storage bits are also called 'internal outputs' or 'internal coils'. They are usually used for internal purposes such as counters, timers, and intermediate output addresses.

(d) Storage registers : are an important part of the data table area since they allow for storage of data words (groups of bits) in BCD or binary format ; they are used to represent input and output data that cannot be represented by single  $^\prime$  1  $^\prime$  0  $^\prime$  bits . Three types , according to their functions , of storage registers exist .

The first type is Input Registers that are used to store multi-bit data received via input interfaces from devices such as shaft encoders or thumb wheel switches. Input registers are also useful for storage of signals from

analog input devices which are converted into equivalent multi-bit binary representation .

The second type is Holding Registers that are used to store constants, entered by the user, or variables, needed during the execution of the user program. Such constants include the timer preset values, counter preset values, and ASCII characters. Timer accumulated values, counter accumulated values, BCD inputs, and BCD outputs are good examples of stored variables.

The third type is Output Registers that are used to store multi-bit data to be transmitted to analog or multi-bit output devices such as speed controllers and control valves .

Figure 2.4 below indicates the four types of memory in the data table areas .

Figure 2.4 Memory Area Types of the Data Table [1] .

### 2.1.3. The-Power Supply:

The power supply is a major part of the PLC . It supplies the DC power required by the CPU and input / output modules; it regulates power supply input to the CPU in order to protect the different components and have a consistent operation of the PLC .

PLCs usually operate with 220 VAC power source . Some PLCs , depending on the application , accept 24 VDC power supply as a voltage source .

There are many factors that might affect the voltage supply in a factory and , thus, affect the voltage input level to the PLC. These include the start up / shut down of some heavy equipment such as large motors or compressors in the site , the power losses due to the various line distances between different substations , and the power losses due to the poor connections in the site [1].

A PLC should be provided with a good power supply that will tolerate some range of variation in the input line voltages, 10 - 15 % for example. However, if the disturbances in the input voltage is higher than that range, the need for a constant voltage transformer, to be connected between the voltage source and the power supply, might arise. The constant voltage transformer will maintain a relatively constant output voltage although its input might be variable.

Moreover , an isolation transformer might be needed to isolate the PLC from the electromagnetic interference (EMI) in the factory that might cause misoperation of the PLC .

Another subject to be considered when thinking of power supplies is the maximum load that can be tolerated; power supplies are capable of providing a maximum amount of current at its terminals, at a given voltage level. If the current required by the different input / output modules, at a moment of time, is greater than the maximum current of the power supply, under-current conditions will result causing an unpredictable operation of the Input / Output system. A previous good knowledge of the application requirements is vital to the selection of the proper power supply.

#### 2.2. The Input / Output System:

The second part of the PLC is the input / output system which constitutes the physical means of communication between the CPU and the outside world . Early PLCs were limited to on / off inputs / outputs . This limitation prevented PLCs from having complete control over some processors which required analog inputs / outputs .

Nowadays , PLCs provide the user with a variety of interfaces suitable for both discrete and analog inputs / outputs . Four different kinds of inputs / outputs will be considered; discrete inputs / outputs , numerical input / outputs , special inputs / outputs , and remote inputs / outputs [1] .

#### 2.2.1. <u>Discrete Inputs / Outputs</u>:

These are the simplest types of inputs / outputs used with PLCs . Discrete input / output interfaces allow the PLC to receive on / off signals from input devices and transmit on / off signals to output devices . A list of

some discrete input / output devices is shown in table 2.1 below .

Table 2.1. Discrete Input / Output Devices .

| Input Devices                                         | Output Devices                  |

|-------------------------------------------------------|---------------------------------|

| - Selector switches - Push buttons - Circuit breakers | - Alarms - Fans - Valves        |

| - Relay contacts - Motor starter contacts             | - Solenoids<br>- Control relays |

Various input / output interface circuits are available for different standard AC and DC voltage ratings. Table 2.2 indicates some of these ratings.

Different AC / DC input interface ratings are available such as 24 , 48 , 120 , and 230 volts AC / DC . The TTL input interfaces allow the PLC to accept signals from TTL-compatible devices , 5 VDC level control devices , and several types of photoelectric sensors .

Non-voltage input interface circuits allow the PLC to accept inputs from devices that are not connected to a power supply. Such interfaces contain their own internal DC ( 24 VDC ) power supply that will compensate for the external power supply.

AC output interface circuits allow the PLC to be able to deal with output devices requiring AC input signals.

Table 2.2 Standard I/O Voltage Ratings of Discrete I/O Interfaces [2] .

| - 12-48 Volts AC     |

|----------------------|

| - 120 , 230 Volts AC |

| - 12-48 Volts DC     |

| - 120 Volts DC       |

| - 23 Volts DC        |

| - Contact relay      |

| - TTL level          |

|                      |

Other discrete input / output interfaces available are outputs .

A typical interface circuit is shown in figure 2.5. The AC / DC input interface circuit normally consists of two DC outputs, contact outputs, TTL outputs, and isolated circuits, the power circuit and the logic circuit; they are usually isolated from each other through a coupler, which can be an optical coupler or pulse transformer, for example.

The power section is responsible for the conversion of the AC input signal to a rectified DC signal via a bridge rectifier , filtering the resulting DC signal to eliminate the dangerous effect of electric noise and signal bouncing , and detecting the minimum threshold level for a valid input signal .

Figure 2.5 Block Diagram for AC / DC Input Circuit [1].

The rectified , filtered signal is coupled through an optical coupler to the logic section of the PLC where it will be used in the control program . The coupler will protect the CPU side from any electrical voltage spikes that might occur .

The logic section of the interface is a digital circuit dealing with digital on  $\!\!\!/$  off signals .

# 2.2.2. <u>Numerical-Data-Inputs-/-Outputs-</u>:

Numerical data input / output interfaces makes it possible for the PLC to control input / output devices that deal with data bits in groups , each of which is considered to be a single unit of data . These devices can be classified into two type : analog devices and digital multi-bit devices . Analog devices transmit / receive analog signals as their outputs / inputs ; such signals include voltages and currents . Temperature transducers , pressure transducers , humidity transducers , and potentiometers are considered to be analog input devices . Analog output devices include analog valves and actuators , analog meters, and electric motor drivers .

Analog input devices need special analog interface

circuits containing analog-to-digital converters and having very high input impedance . Similarly , analog output devices receive signals from the processor through digital-to-analog converters; analog output devices are usually optically coupled to the PLC .

Digital multi-bit devices produce discrete inputs / outputs that cannot be represented by single bits; it rather needs a combination of bits to represent the different levels of its inputs / outputs . Bar code readers and seven-segment displays are good examples of such devices .

Data are received through the input interfaces in groups of bits and are stored in the input registers corresponding to the input devices. The program is executed and the output registers are updated with bits, groups of them, representing in BCD, the output level required. The input / output interfaces in this case provide the PLC with parallel communication capability with the input / output devices.

# 2.2.3. Special Inputs / Outputs:

Apart from discrete and numerical input / output devices which constitute, usually, a high percentage of the devices used in nature, some input / output devices require special input / output interface arrangements to be able to communicate with the PLC. The special input / output interfaces should adapt the signal received or transmitted in a way to suit the input / output device used. Example of signals to be adapted are very low level signals and fast input signals that cannot be detected by

the normal input / output interfaces [1] .

Special I/O arrangements may encounter the use of special I/O interface modules that contain their own processors and RAMs. This is usually called 'Distributed Processing 'since each of the processors at the interface modules accomplishes its tasks independently of the CPU.

The ASCII input / output interface module is a special circuit that requires special attention . Printers and displays , for example , are peripheral devices that send and receive ASCII code through RS-232 or RS-422 communications link . A special I/O interface should be implemented for such a case . If the ASCII interface uses the CPU as a processor, all the handshaking communication protocols are performed by the CPU; this slows down the operation of the PLC since the CPU is interrupted by each input / output character . Moreover , if the scan rate is lower than the rate of communication , some data will be lost; synchronization of the process , thus , might require slowing down the communication process .

Distributed processing solves such a problem; at the start of each scan cycle, the inputs are read including the block of ASCII data accumulated in the I/O interface RAM. The handshaking protocol is performed by the I/O interface processor, and the data transmission between the CPU and the RAM of the I/O module is done at the I/O bus speed.

Similarly , a special network interface module is required to enable the PLC to interact with a network system of different devices in a factory such as robots ,

CNC machines , and CAD / CAM systems via a Local Area Network ( LAN ) . Communication parameters , such as baud rate , and communication protocols are network dependent [1] .

# 2.2.4 Remote Inputs / Outputs:

Large PLCs (512 inputs / outputs or more) provide the user with the capability of having remote input / output subsystems that are still under control of the CPU. Such a configuration requires rack-type enclosures in which the input / output modules are installed and provided with their own power supplies needed in the interface circuitry. A remote input / output adapter module is also needed to allow communications with the processor [1].

Some limitations of remote input / output concept is the maximum number of input / output points in one subsystem and the distance allowed between the CPU and each subsystem.

Remote input  $\!\!\!/$  output modules offer great savings in wire , connections , and labor costs .

#### Chapter Three

### PLC Products and Applications

A variety of PLC products and a variety of PLC applications exist . An overview of these is presented in this chapter .

### 3.1. PLC Families:

Nowadays , different PLC ranges are available with features depending on the size of the controller . These ranges are specified , usually , according to the number of input / output ( I/O ) points provided by the PLC; this is called ' I/O count ' . As the I/O count increases , the complexity , and hence cost , of the system increases , thus requiring an increase in memory capacity , variety in I/O modules , and flexibility of the accompanying software ( instruction set ) [1] .

The PLC products are divided into four ranges (segments) 1 , 2 , 3 , and 4 depending on the variation of the features discussed above . The boundaries of these segments are overlapping with the intersection areas representing PLC products that have the features of the smaller PLC segment enhanced with some features found in the PLCs of the larger segment , thus providing the user with a great flexibility in choice . Figure 3.1 shows the four segments with their overlapping areas .

Segment 1 designates small PLCs which are suitable for simple on / off control . Table A.1.1 in Appendix A.1 shows some of their specifications (features).

Figure 3.1 Illustration of the PLC Product Range [1].

Area 'A' includes small PLCs that are enhanced with features from segment 2 medium controllers; such features include analog control capability, basic mathematical operations handling, LANs compatibility, and remote I/O capability.

Segment 2 PLCs are of medium size and are more flexible than small PLCs. Table A.2.1 in Appendix A.2 indicates their features including analog control capability, data manipulation capability, and arithmetic

capabilities .

Area 'B' represents PLCs with features of segment 2 PLCs enhanced with more memory, PID control capability, subroutine handling capability, and more instructions for arithmetic and data handling.

Segment 3 designates large PLCs having the ability to perform extensive data manipulation , data acquisition , and reporting . Table A.3.1 in Appendix A.3 indicates their features .

Area 'C' represents PLCs having the features of large PLCs with enhanced mathematical and data handling capabilities; they are supported with larger memory and I/O capabilities.

Segment 4 represents very large PLCs that are used in complex control tasks where remote I/O and special I/O interfaces are needed . Table A.4.1 in Appendix A.4 indicates their features .

## 3.2. Defining the Control System:

Users usually face the problem of selecting the suitable PLC to their applications. The user decision should take into consideration many variables including the wide range of PLCs with different features and capabilities, the user's different applications, and thoughts of future expansion.

When a user is in a position to take a decision about the suitable controller , the following should be considered [1]:

1- The I/O modules suitable for the application should be determined . The following six key points should be

considered when determining the system I/O requirements:

- ( a ) the size of the system in terms of the number of different inputs and outputs ,

- ( b ) the remote I/O requirements of the system , including a physical layout of the sensors and actuators ,and information about the largest remote distance from the CPU ,

- ( c ) types of I/O modules required ,

- ( d ) input-to-output response time required ,

- ( e ) diagnostics required , and

- ( f ) redundancy requirements .

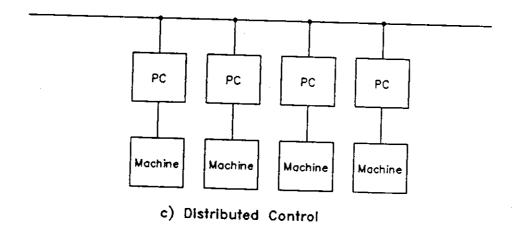

- 2- The user should, according to the knowledge of the application, determine the type of control to be implemented in his / her application. Different types of control exist, each of which has its own advantages, disadvantages, costs, and features; these include individual machine control, centralized control, and distributed control. Figure 3.2 shows the different types of control mentioned [1].

- 3- The user should make a good estimate of the memory size required based on the application size . The type of memory should also be determined; for example, volatile with battery backup, non-volatile, or a combination of both.

Care should be given to limitations of memory provided by the manufacturer; some memory may be limited in the number of internal outputs that can be used. Some restrictions might also be placed on the number of timers / counters used (50, for example).

4- Software is an essential part of the decision making

# a) individual Machine Control

Figure 3.2 Control Type Configurations : a)

Individual Machine Control , b) Centralized Control , c)

Distributed Control .

process; depending on the complexity of the application, the user should determine the instruction set to be used.

Good choice of software leads to ease of programming applications .

- 5- Determination of the different peripherals to be connected to the PLC is an important issue; future expansion should be taken into consideration.

- 6- The physical and environmental conditions of the user site might affect the PLC. The PLC manufacturers specifications about the required operational environment should be studied.

To be more specific , effects of temperature , pressure , dust , and vibration on the PLC should be considered .

- 7- The existence of good vendor support is a must . Things to consider include the availability of a good support staff at the vendor's site , capability of the vendor to support training courses , and the provision of a good technical literature ( manuals ) by the vendor .

- 8- A knowledge of the product proven reliability is important; lack of reliability increases machine downtime and affects product quality.

Table 3.1 indicates the major steps and considerations to be taken when selecting a PLC .

## 3.3. Steps to Implement a PLC System:

The methodical and logical approach is the key to success in the implementation of a PLC system . No matter how large the system is , a methodical approach yields reliable outcomes .

First , define your systems functional specifications . Second , draw the process and

Table 3.1 Steps for Selecting the Right PLC [1] .

```

Step 1

Know the process to be controlled .

Step 2

Determine the type of control .

a- Distributed control

b- Centralized control

c- Individual machine control

Determine the I/O interface requirement .

Step 3

a- Estimate digital and analog inputs

and outputs

b- Check for Input/Output specifications

c- Determine if remote I/O is required

d- Special I/O requirements

e- Allow for future expansion

Step 4

Determine software language and functions .

a- Ladder , Boolean , and/or high level

b- Basic instructions ( timers ,

counters , etc)

c- Enhanced instructions / functions

(math , PID)

Step 5

Consider the type of memory .

a- Volatile ( R/W )

b- Non-volatile (EEPROM , EPROM ,

Non-volatile RAM , CORE)

c- Combination of volatile and non-

volatile

Step 6

Consider memory capacity .

a- Estimate memory usage based on memory

utilization per instruction

b- Allow extra memory for complex

programming and future expansion .

Step 7

Evaluate processor scan time requirement

Step 8

Define programming and storage device

requirements .

a- CRT

b- Computer

c- Cassette or disk storage

d- Mini-programmer

e- Consider the functional capabilities

of programming devices

continue

```

Table 1.1 Continued .

```

Step 9 :

Define peripheral requirements .

a- Graphic display

b- Operator interface

c- Line printers

d- Documentation systems

e- Report generation systems

Step 10:

Determine any physical and environmental

constraints .

a- Available space of system

b- Ambient conditions

Step 11: Evaluate other factors that can affect

selection .

a- Vendor support

b- Product proven reliability

c- Plant goals for future

(e.g., standardization)

```

instrumentation ( PI ) diagrams . Third , draw an I/O list . Fourth , draw the PLC configuration diagrams . Next , write the PLC program . Last , document the whole process [6] .

Definition of the systems functional specification is the initial and most important step; other steps greatly depend on it. It should include a clear defintion of the final achievements required in terms of general and specific goals. Moreover, a description of the system operation should be included.

A modular approach can be used to produce the system specification definition . First, a general description of the nature and performance of the plants equipment and of the systems total operation is made . Next , the general

description is broken into smaller functional blocks containing more details . Finally , a sequence list is obtained by providing a real-time description of the sequence of events within each functional block .

The PI diagrams include the process logic and process layout schematic . They show the different plant items , instruments , devices , and PLC I/O . Interconnections in the layout are also shown .

An I/O list is built on the information provided by the PI diagrams . It shows all the devices , their field wiring numbering , and their terminal numbers they will occupy on that PLC .

The PLC configuration diagrams support the I/O list; they show the hardware layout and connections of the racks, CPU, power supply, and I/O cards of the PLC.

The modular approach for writing a PLC program proved to be the most professional; testing of the written code is easy, diagnosis of the code problems is straight forward, and the size of the code is, usually, smaller than other programming methods. Thus, commissioning time is reduced.

Documentation includes all the documents that are made in the previous steps. It also includes an operator's manual. The documentation can be reproduced into a user-friendly set of manuals that will last for future use.

## 3.4. PLC Applications -:

Nowadays , PLCs are successfully applied in most industrial fields including steel milling , food

processing, and chemical and petrochemical treatment. Following is a quick glimpse of some of the PLC applications that would give good insight of the benefits of using PLCs and would stimulate new ideas about where and how to use PLCs [1].

### 3.4.1. Rubber and Plastic:

#### Tire Curing Press Monitoring :

PLCs are used to perform individual press monitoring for time, pressure, and temperature during each press cycle. Machine status information is stored for later report generation and to alert the operator of any press malfunctions [1].

#### Tire Manufacturing:

PLCs are used to control the sequencing of events which must occur to transform the raw tire into a tire fit for the road . Such events , in tire press / cure systems , include molding the thread pattern and the rubber obtain to the road-resistant characteristics Use of PLCs reduces requirement and increases reliability of the system and quality of the product [1] .

#### Plastic Injection Molding :

PLCs are used to control such variables as temperature and pressure for the optimization of the injection molding process. The PLC system provides the closed loop injection to provide good quality; the system can also accumulate production data for future use [1].

### 3.4.2. Chemical and Petrochemical:

#### Ammonia and Ethene Processing

PLCs monitor and control large compressors that are used during the manufacturing of ammonia , ethylene , and other chemicals . The PLC monitors bearing temperatures , operation of clearance pockets , compressor speed , power consumption , vibration , discharge temperatures , pressure , suction flow , and gas composition [1] .

#### Dyes:

PLCs monitor and control the dye processing used in the textile industry. Accurate processing of color blending is provided [1].

#### Gas Transmission and Distribution:

PLCs monitor and regulate pressures and flows of gas transmission and distribution systems [1] .

#### Fan Control:

PLCs automatically control fans based on levels of toxic gases in a chemical production environment. Control of fan start / stop, cycling, and speed is performed by the PLC so as to prevent contamination and to minimize energy consumption [1].

#### 3.4.3. <u>Power-</u>:

#### Plant Power System:

PLCs regulate the proper distribution of available electricity, gas, or steam. Monitoring power house facilities, scheduling distribution of energy, and generating distribution reports is also accomplished by PLCs [1].

### Energy Management:

PLCs control heating and cooling units in a manufacturing plant. Control of load cycles is also performed. Scheduled reports on the amount of energy used by the heating and cooling units are provided [1].

# Compressor Efficiency Control :

PLCs are used to control several compressors by handling safety interlocks, start up / shut down sequences, and compressor cycling. Using non-linear curves of the compressors, they are controlled to run at maximum efficiency [1].

## 3.4.4. <u>Metals</u>:

### Steel Making:

PLCs are used to control furnaces to produce metals according to preset specifications. PLCs also calculate oxygen and power requirements [1].

# Loading and Unloading of Alloys:

PLCs are used to control and monitor quantities of coal, iron ore, and limestone to be melted; this is done through accurate weighing and loading sequences [1].

### Cold Rolling:

PLCs are used to control the conversion of semifinished products into finished products through cold rolling machines . Speed of the motors need to be controlled to obtain correct tension and provide adequate gauging of the rolling material [1] .

## 3.4.5. Materials Handling:

### Storage and Retrieval Systems:

PLCs are used to load and unload parts in storage and retrieval systems. PLCs keep track of necessary information such as storage lane numbers, the parts assigned to specific lanes, and the quantity of parts in any particular lane. This provides quick storage and retrieval of parts. Inventory reports can also be produced [1].

### Automatic Plating Line :

PLCs are used to control set patterns for the automated hoist which can traverse left, right, up, and down through the various plating solutions. PLCs keep track of the hoist location at all times [1].

### Conveyor systems:

PLCs control all the sequential operations, alarms, and necessary logic for circulating parts on a main line conveyor. Optimization of palletizer duty can also be obtained by scheduling lane sorting using PLCs [1].

### Automated Ware-Housing:

PLCs control the movement of stacking cranes; high turn around of materials requests in an automated high cube vertical house is also provided. Aisle conveyors and case palletizers are also controlled by PLCs to reduce manpower requirements significantly [1].

### 3.4.6. Automotive:

Internal Combustion Engine Monitoring:

PLCs monitor engines through monitoring water temperature, oil temperature, RPMs, torque, oil, pressure, and timing; special sensors are located at the internal combustion engine to acquire data [1].

## Carburetor Production Testing :

PLCs are used to test variables such as pressure, vacuum, and flow to provide on-line analysis of automotive carburetors in a production assembly line. Significant reduction in test time, greater yield, and better quality are thus obtained [1].

## Power Steering Assembly and Test:

PLCs are used to control machines that ensure proper balance of valves and maximize left and right tuning ratios [1].

# 3.4.7. Manufacturing /-Machining:

### Production Machines

Control and monitoring of automatic production machines at high efficiency rates is performed by PLCs. Monitoring also encounters machine status and piece count production [1].

### Wire Machines:

The time and on / off cycles of wire drawing machines are monitored using PLCs. Ramping control and synchronization of electric motor drives are also provided by the PLC system [1].

#### Tool Changing:

PLCs are used to control synchronous metal cutting machines with several tool groups. Based on the number of parts that a tool manufactures, the PLC system keeps track of when to change the tool [1].

### 3.4.8. <u>Examples</u>:

## (a) Conveying Systems:

Conveyor Dynamics , Inc. ( CDI ) in U.S.A. has developed a modular approach to PLC programming over several years of accumulated experience in control of crushing and conveying systems . CDI has many successful sites at Canada , Utah , Mexico , Arizona, and Chile in which PLCs were used to efficiently control conveying and crushing systems [7] .

CDI has its own control philosophy that aims at five major goals. First is to maximize system safety. Second is to minimize commissioning downtime. Third is to minimize production down-time and maximize availability. Next is simplifying the operator interface and control. Last is providing fast diagnostics.

Large conveyors control systems should be precisely designed to insure safe operation; dynamic instabilities of the belt, belt drift in curve conveyors, and fast natural acceleration of decline conveyors under loaded conditions are points of issue in such systems.

PLC control systems has proved to be efficient

in this field: they provide precise control of conveyor startup and stoppage sequences, they are flexible to field customization and tuning, and they are capable of monitoring the different components of the system. Thus, a high level of protection is guaranteed.

Smooth transitions from old existing relay control systems to new PLC control systems can be obtained by careful planning, full simulation of the control programs, and efficient debugging of problems, all of which are provided by the new PLC systems. Thus commissioning down-time is reduced.

The development of a reliable , complete diagnostics systems leads to minimizing the production down-time and , hence , maximizing system availability . PLC systems are completely flexible for such developments .

PLC systems can be interfaced to numerous control panels, a combination of which provides a user-friendly, efficient operator interface. Such an operator interface would minimize training time and operator errors.

Proper diagnostics of problems , a feature of PLC systems , results in fast fault finding ; down-time is minimized . It also helps organizing preventive maintenance .

# (b) Monitoring of -Analyzer Systems:

Syncrode Canada Ltd. is using PLCs in monitoring the operation of different analyzer systems .

Abnormal operation conditions are detected and corrective actions are taken to provide proper operation [8].

PLCs are used with flue gas analyzer applications in which the status of the instrument air supply status has to be recorded. Syncrode Canada Ltd. is using PLCs in boiler control systems to monitor inlet flow rate of both sample and combustion air. Moreover, they are using PLCs with analyzer systems to monitor steam quantity in a hydrogen reformer plant.

Syncrode Canada Ltd. is using PLCs due to their flexibility and adaptability. However, it faces some problems since operators are unfamiliar with PLCs and ladder diagram. Many more applications of PLCs in industry really exist, and much more applications appear, every now and then, due to the great facilities that PLCs provide.

## <u>Chapter Four</u> <u>Hardware Design</u>

Based on the information in the previous chapter, the steps towards constructing a prototype PLC are separated into two interrelated procedures to be carried out in parallel. These are the hardware design and software development and programming.

Hardware design is concerned with the construction of a hardware environment similar to that of the PLC. The software procedure is concerned with the development of a suitable software environment related to the hardware part and similar to that of the PLC. This chapter is devoted to the description of hardware design. Chapter five is devoted to software development and programming.

As was described in chapter two , the PLC structure is composed of two major parts: The Central Processing Unit ( CPU ) and the Input / Output ( I/O ) interface. Hardware wise , the construction of a prototype PLC calls for the implementation of these two parts.

# 4.1. Central Processing Unit (CPU):

A personal computer is used to provide the CPU part of a PLC . As it has been previously mentioned , the CPU is composed of three parts; the processor , the power supply, and the memory; which are all provided by the personal computer .

personal computer with an 8086 or an 80286 microprocessor would be sufficient to operate the prototype PLC since our expected applications in the C.I.M. laboratory would never require a more powerful processor .

However, an 80386 or 80486 microprocessor based personal computer can be used, when needed, to get a higher performance.

### 4.2. <u>Input/Output (I/O) Interface</u>:

Since the input / output interface part of the PLC is an application dependent part , a prototype discrete I/O module is designed to provide twelve on / off output signals at 115 VAC and twelve on / off signals at TTL level . The I/O module consists of two major parts : the I/O interface card and the power amplification card .

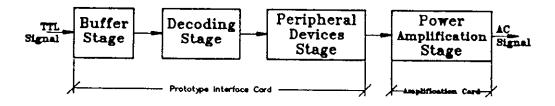

Figure 4.1 is a block diagram of the I/O module implementeed .

Figure 4.1 Block Diagram of the I/O Module .

The interface card is designed to be inserted in any of the personal computer available card slots and is considered to be a part of the personal computer. This prototype card is designed to be used in all personal computer models which use the 62-pin interface bus. This includes the PC-XT and PC-AT. However, this card does not support 16-bit data transfers in the PC-AT; only 8-bit data transfers are supported.

A DC / AC converter ( power amplification ) stage is

designed to receive the output signals of the interface card and , accordingly , provide AC signals capable of driving AC loads . This stage represents , in addition to the I/O interface card , an I/O module suitable for 115 VAC applications .

# 4.2.1. <u>Input / Output Interface Card</u>:

The card is composed of three hardware stages :

- (a) Buffer stage: the buffer stage is designed to protect the personal computer from high current leakages and voltage drops. All the address, data, and control lines are buffered using line drivers and bus transceivers, thus, peripheral devices can be installed in the card securely eliminating undesirable under-current conditions.

- (b) Decoding stage: the decoding stage is designed to decode the buffered address bus signals of the personal computer to determine the peripheral device to be accessed. The buffered control lines such as +AEN , -IOW , and -IOR are also used in the decoding process . Decoding is performed using a comparator , a decoder , AND gates , and OR gates .

- (c) Peripheral devices stage: this stage is designed to have two peripheral devices; these are the 8255A Programmable Peripheral Interface ( PPI ) device and the 8253 Timer / Counter Circuit device. This stage allows for future expansion of six more peripheral devices.

Table 4.1 shows a list of the components used to build-up the interface card .

Figure 4.2 is a schematic diagram of the I/O interface card.

Table 4.1. Components of The Interface Card .

| (           | Component                | Quantity |

|-------------|--------------------------|----------|

| 74LS00 N    | NAND Gates               | 2        |

| 74LS08 A    | ND Gates                 | 1        |

| 74LS85 C    | Comparator               | 1        |

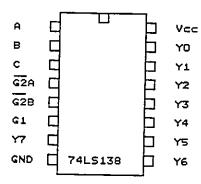

| 74LS138 D   | Decoder                  | 1        |

| 74LS244 I   | Line Driver              | 2        |

| 74LS245 B   | Bus Transciever          | 1        |

| 8255A P     | PI                       | 1        |

| 8253 т      | imer / Counter           | 1        |

| 1 MHz C     | rystal                   | 1        |

| 4 Position  | Dip Switch               | 1        |

| 10 Micro    | Farad Tantalum Capacitor | 2        |

| 0.1 Micro   | Farad Capacitor          | 5        |

| 4.7 kohm R  | esistance                | 5        |

| 1 Kohm Re   | esistance                | 2        |

| 330 ohm res | sistance                 | 1        |

|             |                          |          |

# 4.2.1.1. Buffer Stage:

IC-1 (74LS245) is a bidirectional 8-bit bus transceiver. It operates in a three-state mode and controls the transfer of data between the 62 pin bus and the unique circuitry on the card. The 'Dir' (pin 1 ) on the chip determines the direction of data flow. If it is 'Low', data will flow from the card circuitry to the interface bus; if it is 'High',

data will flow from the interface bus to the card circuitry. The 'Output Enable' (pin 19) controls data flow: when pin 19 is 'Active Low', data will be permitted to flow; else, the 74LS245 switches to its' third' state (high impedance). The 74LS245 data sheets are shown in Appendix B.1 [9].

ICs two and three ( 74LS244 ) are 8-bit wide line drivers whose 'Enable' pins (  $\overline{1G}$  &  $\overline{2G}$  ) are connected to ground. They always pass the bus signals they buffer straight through since their enable signals are 'Active Low'. Refer to Appendix B.2 for the 74LS244 data sheets [9].

# 4.2.1.2. Decoding Stage:

IC-4 ( 74LS85 ) is a four-bit comparator that compares the signals' levels arriving from their logical sources, the address bus ( A8 - A5 ) and the DIP switch, and outputs a 'High' signal (pin6) if they are equal. This chip is enabled by the address line ( A9 ) . The 74LS85 data sheets are shown in Appendix B.3 [9] .

The sixteen different possible positions of the DIP switch provides a wide range of addresses that can be used to access the card . For example , if the DIP switch is positioned at ( 1000 ) , then the range of addresses available is Hex 300 - 31F . Similarly , if switch is positioned at (0000) then the range of addresses available is Hex 200 - 21F . IC-5 (74LS138) is a decoder that further decodes the address line (A4 - A2) . Each of the selected outputs can be used

to enable four consecutive addresses , using A1 and A0 . For example , when the DIP switch is positioned at ( 1000 ) the 'Select 1 'pin will be Active Low for the address range Hex 304 - 307 .

The 74LS138 decoder is enabled when pin 4  $(\overline{G2A})$  is 'Active Low', this will occur if the following conditions are met:

- \* Either -IOR or -IOW is active low ,

- \* +AEN is low,

- \* and the comparator output is 'High' (enabled), thus, indicating the appropriate address selection. Data sheets for the 74LS138 decoder are included in Appendix B.4 [9].

The same conditions are used to control data flow in IC-1. These conditions are controlled using a combination of NAND / AND gates from ICs 8 and 9 (74LS00 and 74LS08, respectively).

## 4.2.1.3. Peripheral Devices Stage:

Two of the selected outputs , 'Select 0' and 'Select 1', are used to chip select IC-7 and IC-6 , respectively .

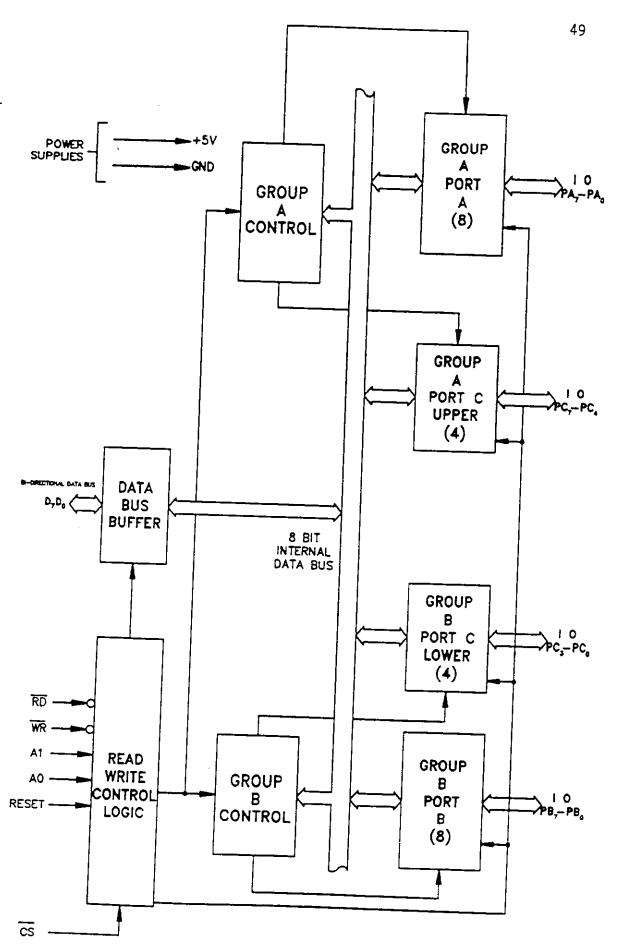

IC-6 is an 8255A Programmable Peripheral Interface ( PPI ) chip that provides parallel data transfer ( I/O ) . It has 24 ( 3 ports A , B , and C ; 8 bits each ) I/O lines which may be individually programmed in two groups of 12 lines each and used in three different modes of operation [10] .

Mode 0 , called 'Basic Input / Output 'mode , is implemented in this card in which each group of 12 I/O pins may be programmed in sets of 4 as either

input or output .

Mode 1 , called 'Strobed Input / Output 'mode, provides two 8-bit data ports that can be configured to operate in either input or output mode in conjunction with strobes or 'hand shaking 'protocols . Port C is divided into two parts , 4-bits each , that work as control and status signals ports for the PPI .

Mode 2 , called 'Strobed Bidirectional Bus I/O', provides the user with one 8-bit bidirectional port accompanied with five control / status signals that specify the instantaneous direction of data flow .

Mode 0 provides simple input and output operations that require no hand shaking procedures . It can be functionally defined as:

- \* Having two 8-bit ports , A and B , and two 4-bit ports , C upper (PC4 PC7) and C lower (PC0 PC3) .

- \* Any port can be input or output ; thus , sixteen different I/O configurations are possible .

- \* Outputs are latched .

- \* Inputs are not latched .

This card uses configuration 12 in which both ports A ( PA7 - PA0 ) and C upper ( PC7 - PC4 ) are used as inputs , and ports B ( PB7 - PB0 ) and C lower ( PC3 - PC0 ) are used as outputs .

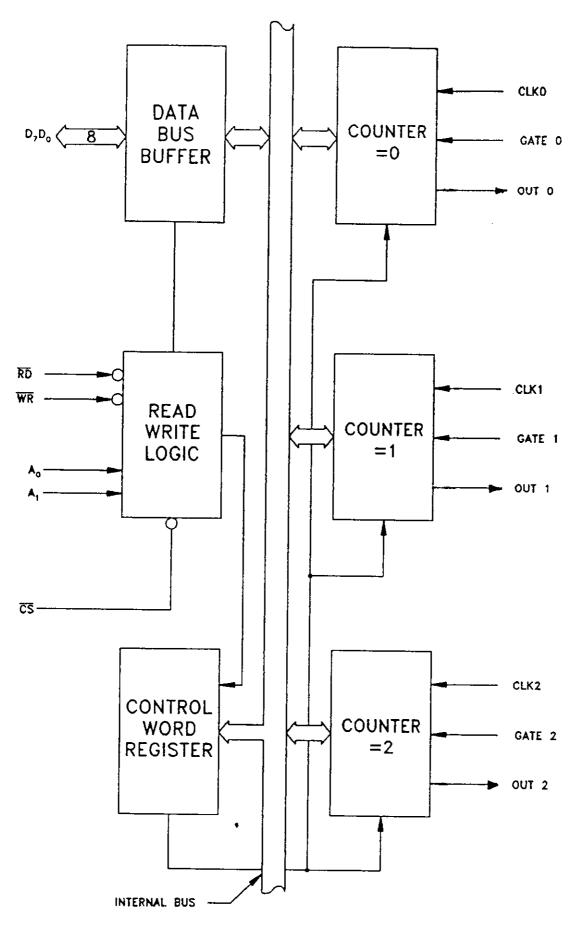

Figure 4.3 shows a block diagram of the PPI; it consists of the following blocks:

1- Data Bus Buffer ( D7 - D0 ) :

This is a three-state bidirectional 8-bit buffer

Figure 4.3 Block Diagram of the PPI [10] .

that is used to interface the 8255A to the system data bus. Direction and time of data flow is controlled by the MPU instructions. This bus is also used to transfer control and status information.

2- Read, Write, and Control Logic:

Upon receiving address and control signals from the Micro Processor Unit ( MPU ) , the control logic block issues commands to the control blocks of both groups , A and B , to manage the internal and

external transfer of data and control words .

This block includes the Chip Select (  $\overline{CS}$  ) pin which , when 'Active Low' enables the 8255A . It also includes the Read (  $\overline{RD}$  ) pin which allows the CPU to read from the 8255A and the Write (  $\overline{WR}$  ) pin which allows the CPU to write to the 8255A . The Port Select 0 and Port Select 1 ( A0 and A1 ) pins which , in coordination with the RD and WR pins control the selection of one of the three ports or the control word registers , are also included in this block . Moreover , this block includes the Reset pin which , when 'Active High' , clears the control registers and sets all ports ( A , B , and C ) to operate at the input mode .

Table 4.2. shows the different possible combinations of the control and address signals and , hence , the resulting operation .

# 3- Group A and Group B Controls:

These control blocks are loaded by the CPU with control instructions that specify the functional

| Table | 4.2 | 8255A | Basic | Operation | f101 |  |

|-------|-----|-------|-------|-----------|------|--|

|-------|-----|-------|-------|-----------|------|--|

| A1 | A0 | RD | WR | <del>cs</del>                         | Operation         |

|----|----|----|----|---------------------------------------|-------------------|

|    |    |    |    |                                       | Input ( READ )    |

| 0  | 0  | 0  | 1  | 0                                     | Port A> Data Bus  |

| 0  | 1  | 0  | 1  | 0                                     | Port B> Data Bus  |

| 1  | 0  | 0  | 1  | 0                                     | Port C> Data Bus  |

|    |    |    |    |                                       | Output ( WRITE )  |

| 0  | 0  | 1  | 0  | 0                                     | Data Bus> Port A  |

| 0  | 1  | 1  | 0  | 0                                     | Data Bus> Port B  |

| 1  | 0  | 1  | 0  | 0                                     | Data Bus> Port C  |

| 1  | 1  | 1  | 0  | 0                                     | Data Bus> Control |

|    |    |    |    | · · · · · · · · · · · · · · · · · · · | Disable Function  |

| х  | x  | x  | x  | 1                                     | Data Bus> 3-State |

| 1  | 1  | 0  | 1  | 0                                     | Illegal Condition |

| X  | х  | 1  | 1  | 0                                     | Data Bus> 3-State |

configuration of each port . Upon receiving signals from the Read / Write Control Logic , each control block issues proper commands to its associated ports. Control Group A controls port A and C upper ( PC7 - PC4 ) ; Control Group B controls port B and port C lower ( PC3 - PC0 ) .

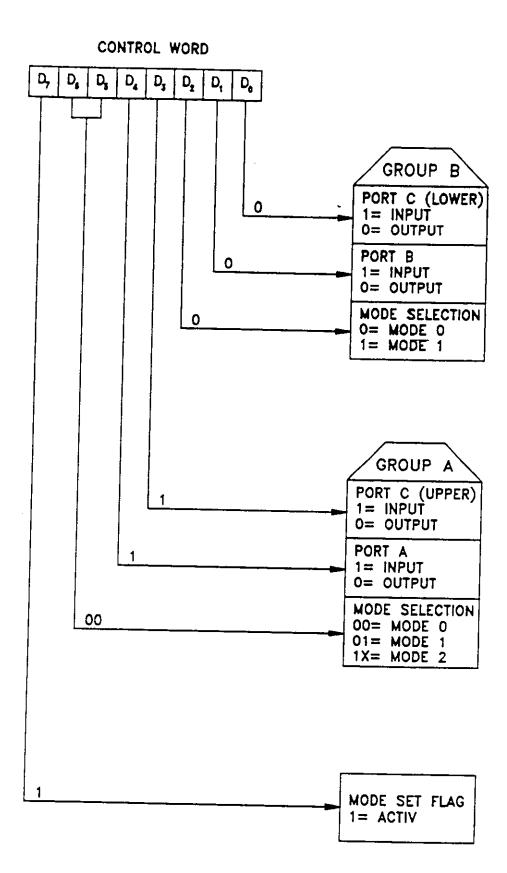

The control information is determined by a control word transmitted by the CPU . Figure 4.4 shows the mode definition format of the control word.

Our control word for mode 0 configuration is (10011000).

### 4- Ports A , B , and C :

The PPI has three ports with the following specifications:

Port A: One 8-bit data output latch / buffer and one 8-bit data input latch .

PORT B : One 8-bit data input / output latch / buffer and one 8-bit data input buffer .

PORT C: One 8-bit data output latch / buffer and one 8-bit data input buffer (no latch for input).

This port can be divided into two 4-bit ports under the mode control .

Table 4.3 shows the PPI port definition format at mode 0 operation .

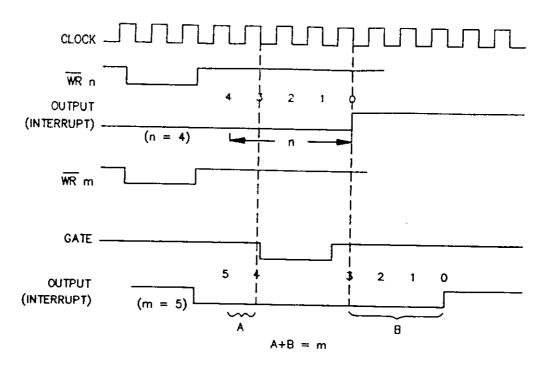

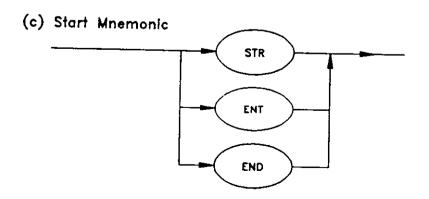

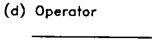

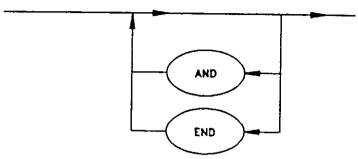

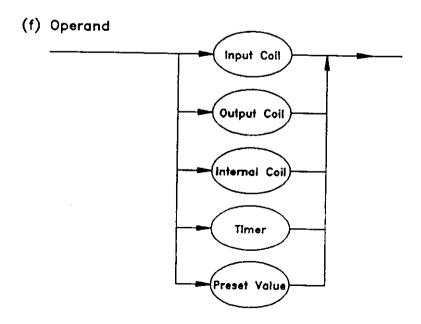

IC-7 (8253) is a programmable interval timer / counter that includes three identical 16-bit counters which can operate independently in any of six different modes . To operate a counter , an (8 / 16)loaded in its register and , -bit count is command, it begins to decrement the count until it reaches zero. At the end of the count , it generates that can be detected by the CPU at one of a pulse its available interrupt requests ( IRQ6 ) or by any available input port ( PC#5 of PPI is used in our case ) . In addition , the count can be read by the cpu while the counter is decrementing [10] .